Intel hat auf der IEEE International Solid-State Circuits Conference (ISSCC) in San Francisco einen Spezialprozessor vorgestellt, der verschlüsselte Daten verarbeitet, ohne sie jemals zu entschlüsseln. Wie IEEE Spectrum berichtet, nutzt der sogenannte Heracles-Chip vollhomomorphe Verschlüsselung (FHE) und erzielt dabei gegenüber einer handelsüblichen Intel-Xeon-Server-CPU Geschwindigkeitssteigerungen zwischen dem 1.074- und 5.547-fachen. Damit könnte eine Technologie, die bislang vor allem aufgrund ihrer Trägheit auf Allzweckprozessoren kaum praxistauglich war, erstmals in großem Maßstab einsetzbar werden.

Vollhomomorphe Verschlüsselung: Prinzip und bisherige Einschränkungen

Vollhomomorphe Verschlüsselung (FHE) erlaubt es, Berechnungen direkt auf verschlüsselten Daten durchzuführen – ohne dass diese an irgendeinem Punkt im Prozess entschlüsselt werden müssen. Das Verfahren lässt sich mathematisch als Transformation beschreiben, ähnlich der Fourier-Transformation: Es verschlüsselt Daten mit einem quantencomputerresistenten Algorithmus und nutzt dabei gezielt die mathematischen Eigenschaften gängiger Rechenoperationen, sodass diese auf den verschlüsselten Daten dasselbe Ergebnis liefern wie auf den unverschlüsselten Ausgangsdaten.

Für Anwendungen, die mit vertraulichen Daten arbeiten, ist das ein grundlegender Vorteil:

Angriffsvektoren wie Seitenkanalangriffe, DMA-Angriffe oder das Mitlesen durch Hypervisoren werden dadurch strukturell ausgeschlossen, weil im Prozessor schlicht keine Klartextdaten vorliegen.

Mögliche Einsatzgebiete reichen von cloudbasierten KI-Anfragen über die Auswertung genetischer Gesundheitsrisiken bis hin zu sicheren Datenbankabfragen im Behördenbereich.

Das Verfahren ist jedoch ausgesprochen rechenintensiv. Auf herkömmlichen CPUs und GPUs dauern FHE-Operationen typischerweise tausend- bis zehntausendmal länger als die Verarbeitung unverschlüsselter Daten. Die Gründe dafür sind vielschichtig:

- FHE-Verschlüsselung lässt die Datenmenge gegenüber dem Klartext um mehrere Größenordnungen anwachsen – ein Chiffretext kann ein Vielfaches des ursprünglichen Datenvolumens umfassen

- Additions- und Multiplikationsoperationen benötigen rund 10.000 zusätzliche Taktzyklen, da FHE mit sehr großen Zahlen arbeitet, die eine hohe Berechnungsgenauigkeit erfordern

- CPUs sind nicht für die parallele Verarbeitung solcher Operationen ausgelegt; GPUs wiederum optimieren von Generation zu Generation zunehmend auf Rechengeschwindigkeit auf Kosten der Präzision – was FHE-Berechnungen unbrauchbar machen kann

- Spezifische Operationen wie „Twiddling“ und „Automorphismus“ sowie das rauschunterdrückende Verfahren „Bootstrapping“ lassen sich auf Allzweckprozessoren kaum effizient abbilden

Zwar haben clevere Softwarebibliotheken und algorithmische Verbesserungen die Lage schrittweise verbessert, doch für großskalige Anwendungen bleibt der Bedarf an dedizierter Hardware bestehen – so das Fazit von IEEE Spectrum.

Heracles: Entstehung und Architektur

Der Heracles-Chip entstand im Rahmen eines DARPA-Förderprogramms und wurde über fünf Jahre als systemweite Initiative entwickelt – beginnend bei der mathematischen Theorie und den Algorithmen bis hin zum konkreten Schaltungsdesign. Gefertigt wird er in Intels 3-Nanometer-FinFET-Technologie, was ihn mit rund 200 mm² Chipfläche etwa zwanzigmal so groß macht wie vergleichbare FHE-Forschungschips, die üblicherweise im Bereich von 10 mm² oder weniger liegen, wie IEEE Spectrum anmerkt.

Flankiert wird der Prozessor von zwei 24-Gigabyte-Hochbandbreitenspeicherchips in einem flüssigkeitsgekühlten Gehäuse – eine Konfiguration, die sonst vor allem bei GPUs für das Training von KI-Modellen anzutreffen ist.

Eine frühe Grundsatzentscheidung des Entwicklungsteams prägte die gesamte Architektur: Statt auf 64-Bit-Arithmetik zu setzen, arbeitet Heracles intern mit 32-Bit-Blöcken. Große Zahlen werden dabei in unabhängig voneinander berechenbare Segmente aufgeteilt. Das verkleinert die Arithmetikschaltkreise erheblich, ermöglicht ein höheres Maß an Parallelverarbeitung und hält dabei die für FHE erforderliche Berechnungsgenauigkeit aufrecht.

Die wichtigsten Architekturmerkmale im Überblick:

- 64 Rechenkerne (sogenannte Tile-Pairs) in einem 8×8-SIMD-Raster, ausgelegt auf die parallele Ausführung von Polynomberechnungen, Twiddling und weiteren FHE-spezifischen Operationen

- 2D-Mesh-Netzwerk mit 512-Byte-Bussen zur Verbindung der einzelnen Kacheln

- 48 GB Hochbandbreitenspeicher mit einer Anbindungsgeschwindigkeit von 819 GB/s

- 64 MB On-Chip-Cache mit einer internen Datenrate von 9,6 TB/s

- Drei synchronisierte Befehlsströme, die Datenübertragung zum und vom Chip, Datenübertragung innerhalb des Chips sowie Rechenoperationen voneinander trennen und so gegenseitige Blockierungen vermeiden

- Taktrate: 1,2 GHz

Benchmarks aus der Live-Demonstration

Auf der ISSCC demonstrierte Intel den Chip anhand einer simulierten Wahlprüfung, über die IEEE Spectrum ausführlich berichtet: Eine verschlüsselte Wähler-ID wird mit einer ebenfalls verschlüsselten Datenbank abgeglichen – ohne dass die Daten zu irgendeinem Zeitpunkt im Klartext vorliegen. Die Wählerin verschlüsselt ihre ID sowie ihre abgegebene Stimme mithilfe von FHE und sendet diese an den Server. Dort ermittelt das System, ob eine Übereinstimmung vorliegt, und gibt eine verschlüsselte Antwort zurück, die ausschließlich die anfragende Person entschlüsseln kann.

Das Ergebnis im direkten Vergleich:

- Intel Xeon (24 Kerne, 3,5 GHz): 15 Millisekunden pro Abfrage

- Heracles: 14 Mikrosekunden pro Abfrage

Für einen einzelnen Vorgang ist der Unterschied kaum wahrnehmbar. In der Summe ergibt sich jedoch ein anderes Bild: Die Überprüfung von 100 Millionen Stimmzetteln würde auf der Xeon-CPU mehr als 17 Tage Rechenzeit in Anspruch nehmen – Heracles würde dieselbe Aufgabe in rund 23 Minuten abschließen.

Bei der zentralen mathematischen Kerntransformation von FHE benötigt Heracles lediglich 39 Mikrosekunden, was einer 2.355-fachen Verbesserung gegenüber der Xeon-CPU entspricht. Über sieben gemessene Schlüsseloperationen liegt der Beschleunigungsfaktor insgesamt zwischen dem 1.074- und 5.547-fachen. Die Streuung erklärt sich laut IEEE Spectrum durch die unterschiedliche Datenbewegung der einzelnen Operationen: Je mehr Daten zwischen Speicher und Rechenkernen bewegt werden müssen, desto stärker bestimmt die Speicherbandbreite das Ergebnis.

Wettbewerb und Marktlage

Intel ist nicht der einzige Akteur in diesem Bereich. Mehrere Start-ups, die teils aus demselben DARPA-Programm hervorgegangen sind, entwickeln konkurrierende Ansätze – wie IEEE Spectrum im Rahmen seiner Berichterstattung darlegt:

- Duality Technology legt den Schwerpunkt auf Softwareprodukte für verschlüsselte Datenbankabfragen und demonstrierte vergangenes Jahr ein FHE-verschlüsseltes Sprachmodell auf Basis der BERT-Architektur. Laut CTO Kurt Rohloff, der die Heracles-Ergebnisse als solide bewertet, liegt der eigentliche Bedarf an spezialisierter Hardware vor allem bei rechenintensiveren KI-nahen Anwendungen – etwa neuronalen Netzen, großen Sprachmodellen oder semantischer Suche.

- Niobium Microsystems (Dayton, Ohio) plant nach eigenen Angaben den weltweit ersten kommerziell verfügbaren FHE-Beschleuniger. Das Unternehmen hat einen Entwicklungsvertrag mit dem südkoreanischen Chipdesigner Semifive unterzeichnet; die Fertigung soll in Samsungs 8-Nanometer-Prozess erfolgen. Konkrete Markteinführungstermine wurden bislang nicht genannt.

- Optalysys verfolgt einen grundlegend anderen Ansatz: Statt rein digitaler Schaltkreise setzt das Unternehmen auf einen photonischen Chip, dessen physikalische Eigenschaften die rechenintensiven Transformationsschritte von FHE übernehmen sollen. CEO Nick New sieht in Heracles eine Annäherung an das, was mit volldigitalen Systemen erreichbar ist – und will diese Grenze mit seinem Ansatz deutlich überschreiten. Ein kommerzieller 3D-gestapelter Chip mit integriertem Silizium für die übrigen Verarbeitungsschritte wird in zwei bis drei Jahren erwartet.

- Fabric Cryptography, Cornami und weitere Start-ups sind ebenfalls in diesem Segment aktiv.

Intel selbst hat bislang keine konkreten Pläne zur Vermarktung von Heracles bekanntgegeben. Niobium sieht darin einen Wettbewerbsvorteil und geht davon aus, den Markt vor dem Technologieriesen zu erschließen.

Ausblick

Für Intel markiert Heracles nach Angaben von Sanu Mathew, der die Sicherheitsschaltungsforschung im Unternehmen leitet, den Beginn einer längeren Entwicklungsreihe – vergleichbar mit dem ersten Mikroprozessor. Das Unternehmen will die Softwareoptimierung weiterführen, sich an umfangreichere FHE-Anwendungsfälle heranwagen und Verbesserungen für eine mögliche Folgegeneration erforschen.

Ro Cammarota, der das Projekt bis Ende 2024 leitete und inzwischen an der University of California Irvine tätig ist, zieht gegenüber IEEE Spectrum eine positive Bilanz: Alle ursprünglich gesteckten Ziele seien vollständig erreicht worden. Ob und wann ein kommerzielles Produkt folgt, bleibt offen.

Quelle: IEEE Spectrum

Auch interessant:

Bild/Quelle: https://depositphotos.com/de/home.html

Fachartikel

KadNap: Wie ein neues Botnetz tausende Asus-Router als Proxy-Knoten missbraucht

ClickFix-Variante nutzt WebDAV und trojanisierte Electron-App zur Malware-Verteilung

KI im SAP-Custom-Code: Sicherheitsrisiken erkennen und gezielt absichern

Zero-Day-Exploits 2025: 90 Schwachstellen, mehr Unternehmensziele, KI als neuer Faktor

Brainworm: Wenn KI-Agenten durch natürliche Sprache zur Waffe werden

Studien

Drucksicherheit bleibt in vielen KMU ein vernachlässigter Bereich

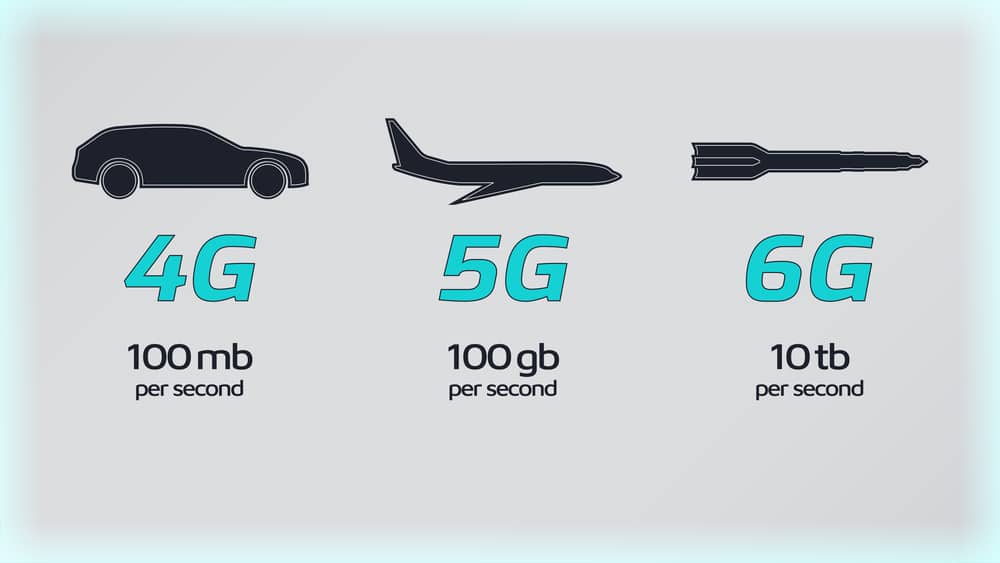

Sieben Regierungen einigen sich auf 6G-Sicherheitsrahmen

Lieferkettenkollaps und Internetausfall: Unternehmen rechnen mit dem Unwahrscheinlichen

KI als Werkzeug für schnelle, kostengünstige Cyberangriffe

KI beschleunigt Cyberangriffe: IBM X-Force warnt vor wachsenden Schwachstellen in Unternehmen

Whitepaper

Cloudflare Threat Report 2026: Ransomware beginnt mit dem Login – KI und Botnetze treiben die Industrialisierung von Cyberangriffen

EBA-Folgebericht: Fortschritte bei IKT-Risikoaufsicht unter DORA – weitere Harmonisierung nötig

Böswillige KI-Nutzung erkennen und verhindern: Anthropics neuer Bedrohungsbericht mit Fallstudien

Third Party Risk Management – auch das Procurement benötigt technische Unterstützung

EU-Toolbox für IKT-Lieferkettensicherheit: Gemeinsamer Rahmen zur Risikominderung

Hamsterrad-Rebell

Sicherer Remote-Zugriff (SRA) für Operational Technology (OT) und industrielle Steuerungs- und Produktionssysteme (ICS) – Teil 2

Incident Response Retainer – worauf sollte man achten?

KI‑basierte E‑Mail‑Angriffe: Einfach gestartet, kaum zu stoppen

NIS2: „Zum Glück gezwungen“ – mit OKR-basiertem Vorgehen zum nachhaltigen Erfolg