Der vom Fraunhofer IPMS entwickelte Prozessorkern EMSA5-FS für funktionale Sicherheit auf Basis der Open-Source-Befehlssatzarchitektur RISC-V wird durch ein weiteres wichtiges Debugging-Tool unterstützt. Mit der Integration in die Toolsets des führenden Herstellers von Mikroprozessor-Entwicklungswerkzeugen Lauterbach stehen nun zahlreiche Debug-Funktionen für den 32-Bit RISC-V Core zur Verfügung.

Der EMSA5-FS ist der erste fehlertolerante Embedded RISC-V-Prozessorkern nach funktionaler Sicherheit und wurde von der Fachzeitschrift Elektronik als Produkt des Jahres 2022 im Bereich Automotive ausgezeichnet. Nun gab der Entwickler, das Fraunhofer-Institut für Photonische Mikrosysteme IPMS, bekannt, dass ein weiterer wichtiger Debugger für den Prozessorkern verfügbar ist. Das TRACE32-Toolset von Lauterbach, dem Weltmarktführer für Hardware-gestützte Debugging-Tools, unterstützt nun auch den EMSA5-FS und bietet Entwicklern umfangreiche Debugging-Funktionen. Der EMSA5-FS-Prozessorkern war der erste RISC-V-Prozessorkern, der als ASIL-D ready nach Automotive Functional Safety zertifiziert wurde und sich damit für den Einsatz in sicherheitskritischen Systemen im Fahrzeug eignet. Er kann sowohl für jede FPGA-Plattform zur Verfügung gestellt als auch in kundenspezifische ASICs für eine breite Palette von Foundry-Technologien integriert werden. Das Fraunhofer IPMS bietet auch Dienstleistungen an, um den IP-Kern mit kundenspezifischen Modulen zu erweitern.

»Die Aufnahme des EMSA5-FS-Prozessorkerns in Lauterbachs TRACE32-Toolset ist für uns ein wichtiger Meilenstein«, erklärt Marcus Pietzsch, Leiter der Gruppe IP-Cores und ASIC-Design am Fraunhofer IPMS. »Durch die enge Zusammenarbeit mit Lauterbach können wir Entwicklern nun zusätzliche Funktionalität rund um das Debugging von Software auf dem RISC-V IP anbieten. Entwickler, die mit unserem Prozessorkern arbeiten, profitieren so von den Vorteilen der Arbeit mit einem erstklassigen Werkzeug.«

Das TRACE32-Toolset von Lauterbach bietet Multicore-Debugging auf einzelnen Hardware-Threads von RISC-V-Cores und ermöglicht das Debugging direkt vom Reset-Vektor aus, der für den Test von Startup-Codes und anderen Schlüsselfunktionen benötigt wird. Lauterbach bietet auch High-Level- und Assembler-Debugging für eine Vielzahl von Standard-ISA-Erweiterungen, wie z.B. Compressed Instructions und Floating Points. Darüber hinaus wird das JTAG-Debug-Transportmodul (DTM) vollständig unterstützt. Der EMSA5-FS eignet sich für die Implementierung von Mikrocontrollern in der Automobilindustrie, der Luft- und Raumfahrt, der Medizintechnik und anderen sicherheitskritischen Geräten und Systemen.

Fachartikel

Studien

Cloud-Transformation & GRC: Die Wolkendecke wird zur Superzelle

Threat Report: Anstieg der Ransomware-Vorfälle durch ERP-Kompromittierung um 400 %

Studie zu PKI und Post-Quanten-Kryptographie verdeutlicht wachsenden Bedarf an digitalem Vertrauen bei DACH-Organisationen

Zunahme von „Evasive Malware“ verstärkt Bedrohungswelle

Neuer Report bestätigt: Die Zukunft KI-gestützter Content Creation ist längst Gegenwart

Whitepaper

Unter4Ohren

Datenklassifizierung: Sicherheit, Konformität und Kontrolle

Die Rolle der KI in der IT-Sicherheit

CrowdStrike Global Threat Report 2024 – Einblicke in die aktuelle Bedrohungslandschaft

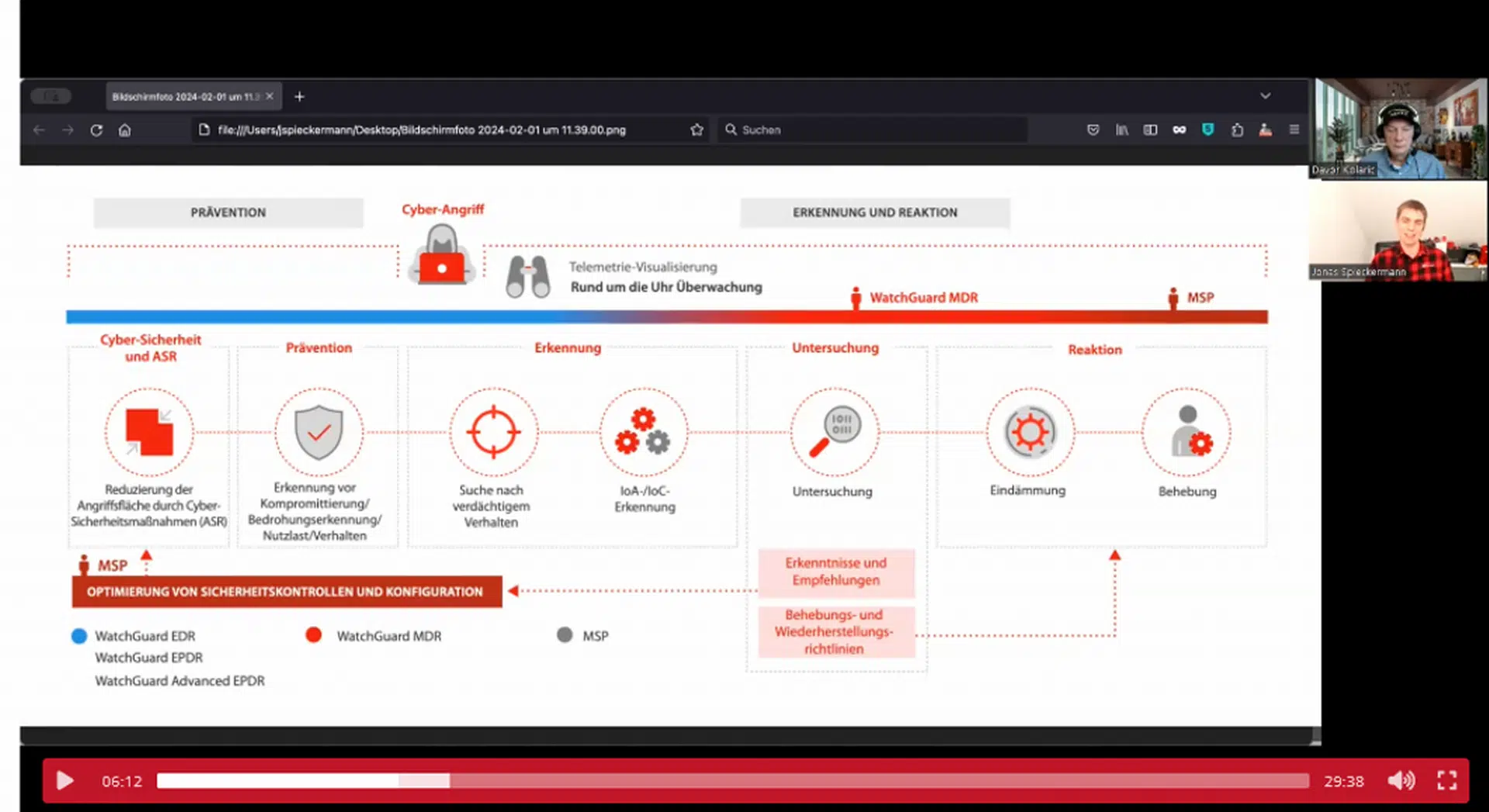

WatchGuard Managed Detection & Response – Erkennung und Reaktion rund um die Uhr ohne Mehraufwand